- 2024-05-05 14:56 942

- 产品价格:1.50 元/个 起

- 发货地址:广东深圳 包装说明:不限

- 产品数量:9999.00 个产品规格:不限

- 信息编号:227217176公司编号:1110848

- 项经理 经理 微信 18922859761

- 进入店铺 在线留言 QQ咨询 在线询价

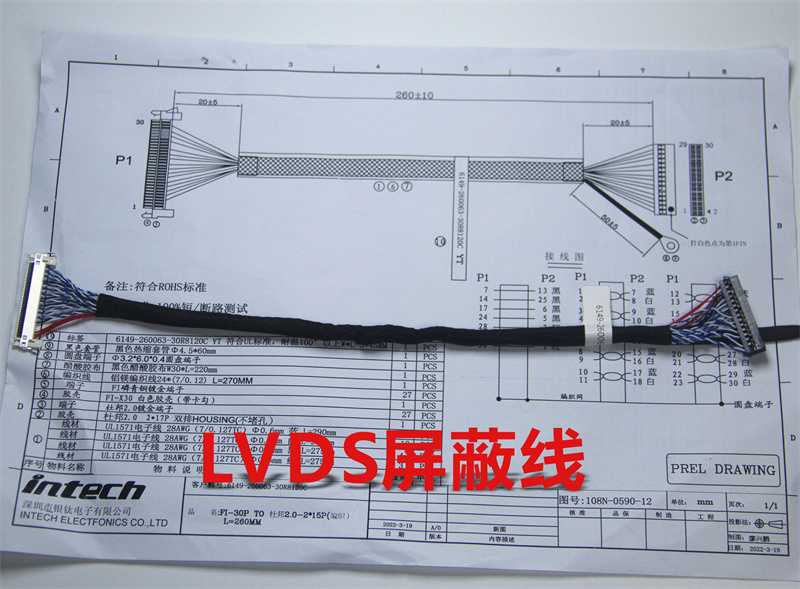

钦州LVDS线报价_生产厂家

- 相关产品:

用途:电子产品材质:PVC发货时间:7-10天销售范围:全国市场适用场景:电器产品机内连接

LVDS线走短线、直线。为确保信号的质量,LVDS差分对走线应该尽可能地短而直,减少布线中的过孔数,避免差分对布线太长,出现太多的拐弯,拐弯处尽量用45°或弧线,避免90°拐弯。LVDS分外层微带线差分模式和内层带状线差分模式两种,分别如图2、图3所示。通过合理设置参数,阻抗可利用相关阻抗计算软件(如POLAR-SI6000、CADENCE的ALLEGRO)计算也可利用阻抗计算公式计算。

LVDS线器件是用CMOS工艺实现的,而CMOS能够提供较低的静态功耗;当恒流源的驱动电流为3.5mA,负载(100Ω终端匹配)的功耗仅为1.225mW;LVDS的功耗是恒定的,不像CMOS收发器的动态功耗那样相对频率而上升。恒流源模式的驱动设计降低了系统功耗,并大地降低了频率成分对功耗的影响。虽然当速率较低时,CMOS的功耗比LVDS小,但是随着频率的提高,CMOS的功耗将逐渐增加,终需要消耗比LVDS更多的功率。通常,当频率等于200MSps时,LVDS和CMOS的功耗大致相同。

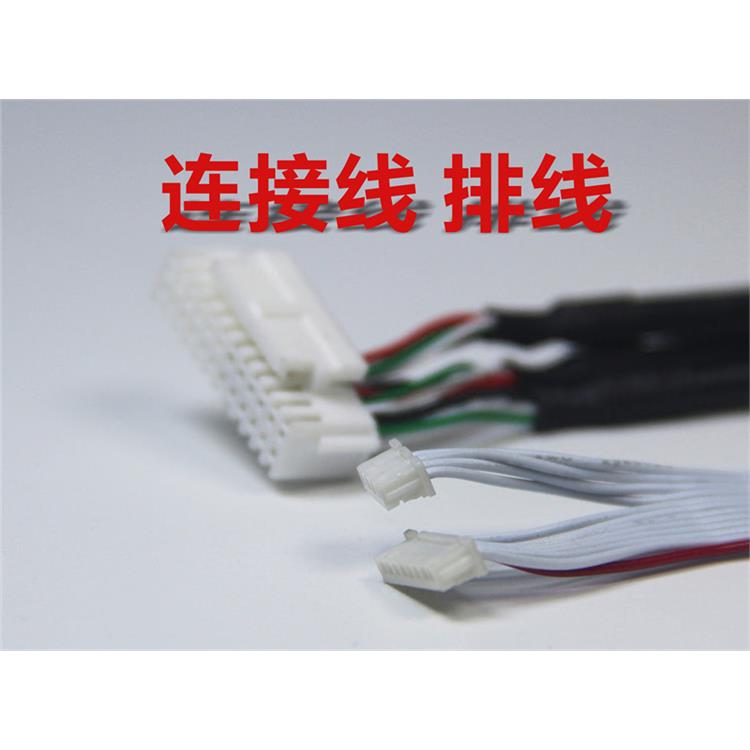

排线具有更高的装配可靠性和质量。排线减少了内连所需的硬体,如传统的电子封装上常用的焊点、中继线、底板线路及线缆,使排线可以提供更高的装配可靠性和质量。因为复杂的多个系统所组成的传统内连硬体在装配时,易出现较高的元件错位率。排线的刚度低,体积小,也正是因为排线板元件的体积较小,所以使用的材料也就少。随着质量工程的出现,一个厚度很薄的挠性系统被设计成仅以一种方式组装,从而消除了许多通常与立布线工程有关的人为错误。

有LVDS信号的印制板一般都要布成多层板。由于LVDS信号属于高速信号,与其相邻的层应为地层,对LVDS信号进行屏蔽防止干扰。另外密度不是很大的板子,在物理空间条件允许的情况下,将LVDS信号与其它信号分别放在不同的层。例如,对于四层板,通常可以按以下进行布层:LVDS信号层、地层、电源层、其它信号层。

深圳市银聚电子有限公司本着“以质取胜于人,以诚取信于人”的经营理念。愿与各界新老朋友携手合作,共话未来!

- 产品分类

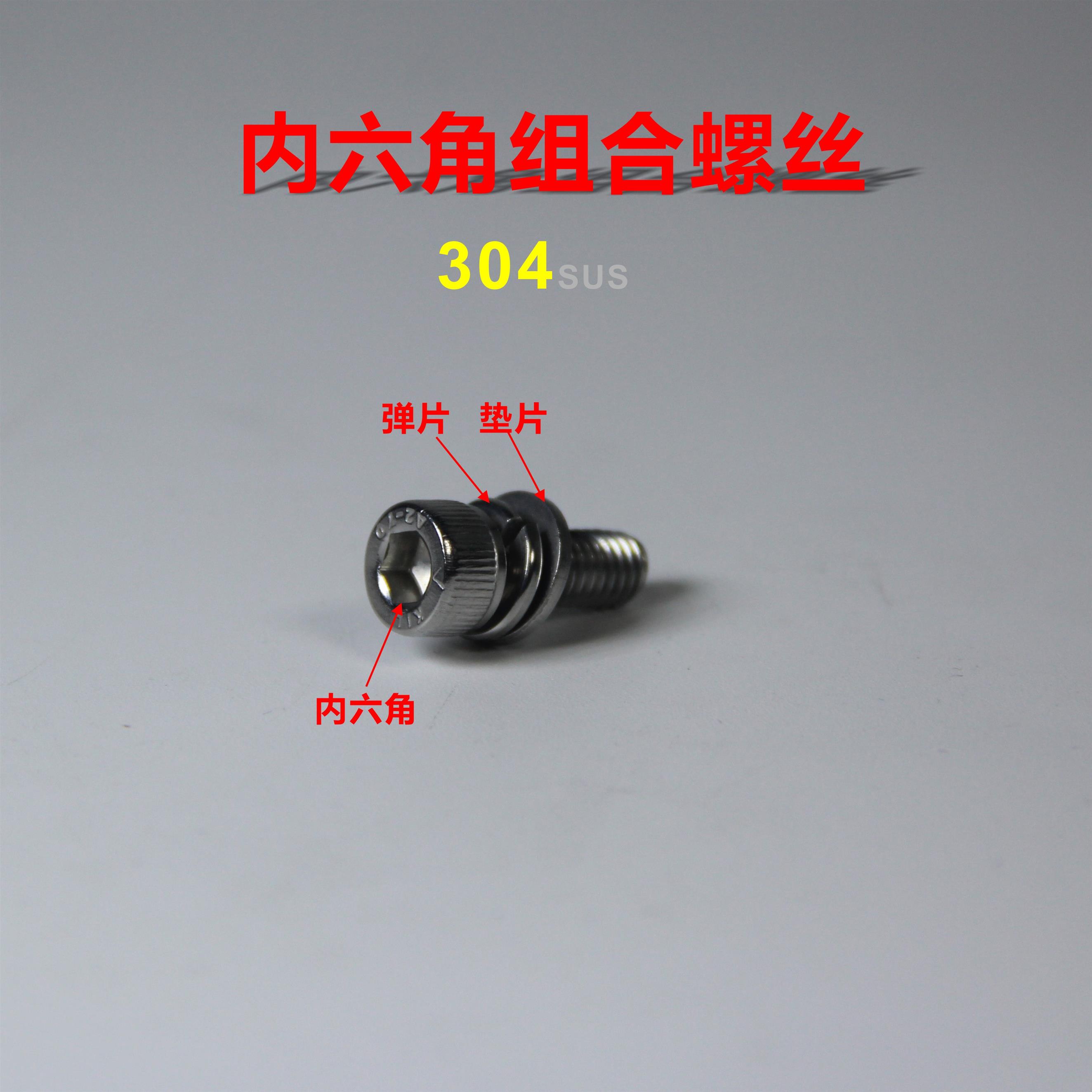

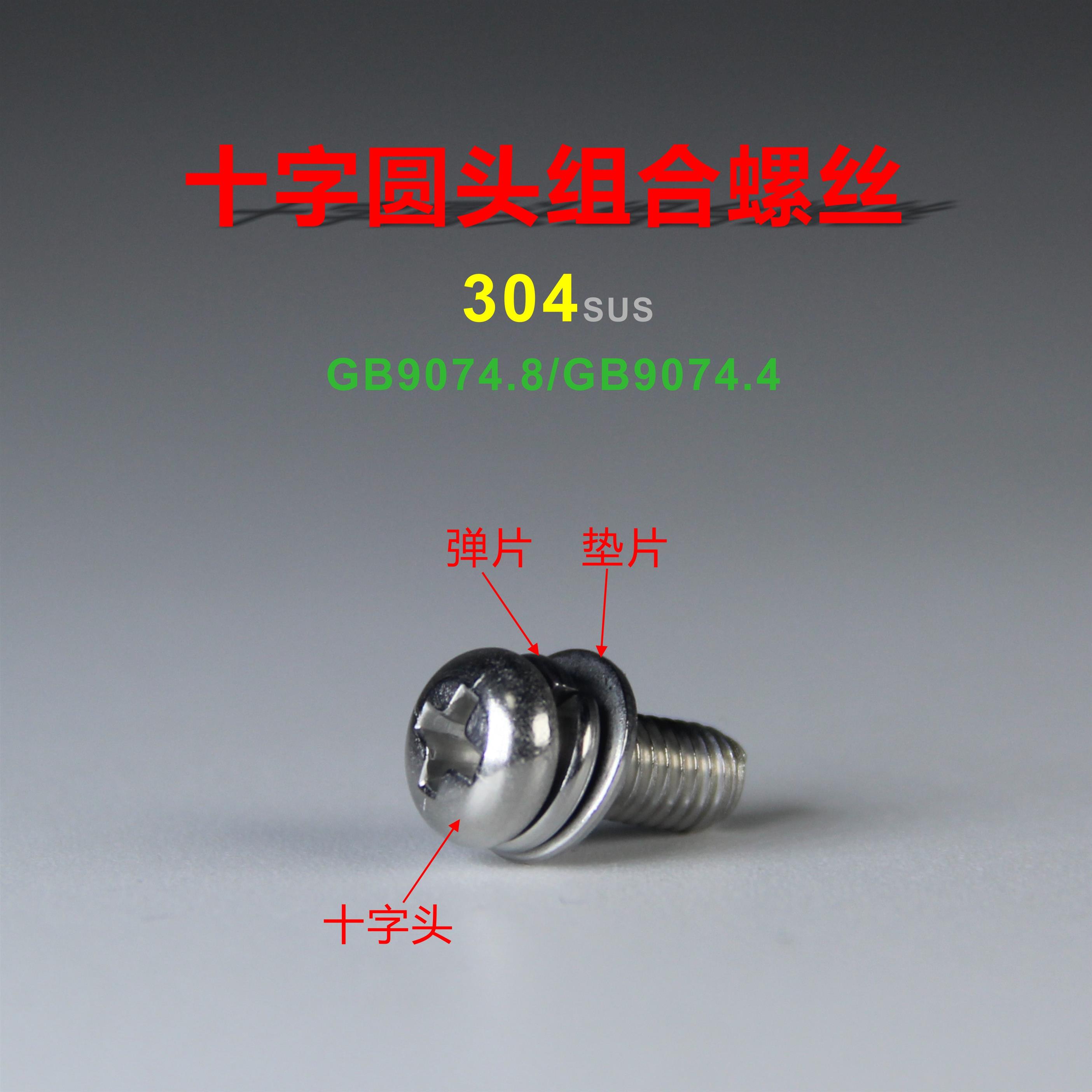

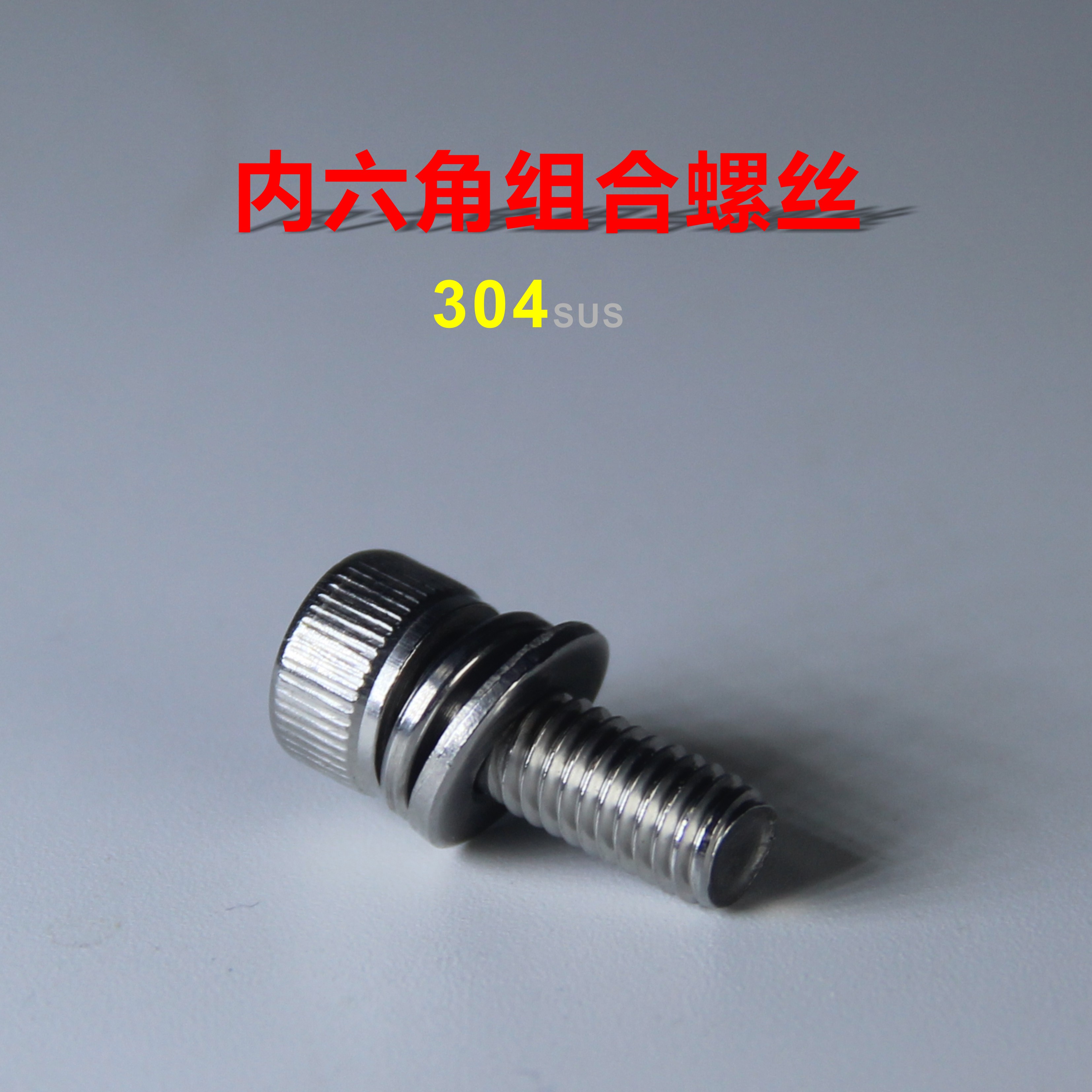

- 螺丝 连接线排线 LVDS线 玻璃陶瓷面板钻孔扫边砂轮